用量子处理器实现拓扑有序态

2021/10/14

拓扑序的非局域性使得被编码到拓扑有序基态上的量子信息对局域的扰动具有鲁棒性,因此有望用于容错量子计算。然而,实现和表征拓扑有序态要求在大二维晶格上能做高保真度的量子门操作,还需要实现长程纠缠,具有很大的挑战性。

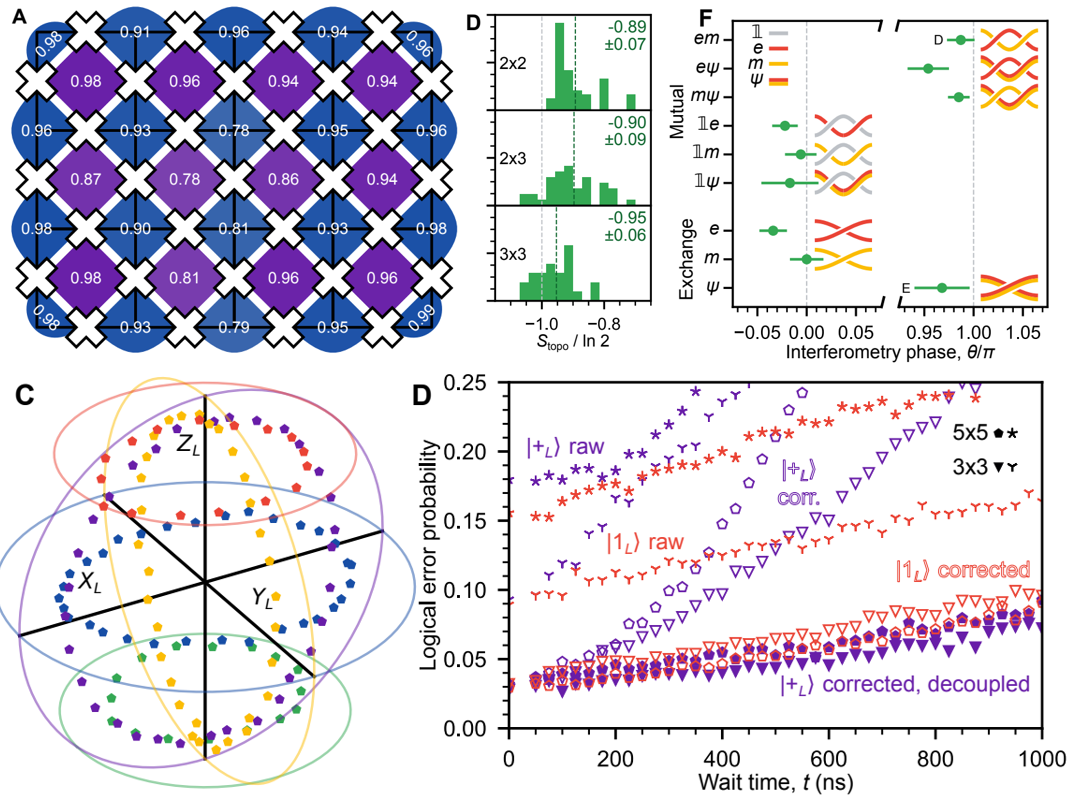

近日,谷歌量子AI团队基于Sycamore量子处理器,在包含31个超导量子比特的晶格上用H门和CZ门制备了环曲面码的基态,且电路深度和系统宽度是线性关系,便于扩展。通过随机单比特门采样,并用迭代贝叶斯方法缓解错误,可以得到二次Renyi熵,发现几种不同子晶格的拓扑纠缠熵都接近-ln2,证明拓扑序存在。接下来用一系列门实现了braiding操作,并用多比特Ramsey,把积累的相位转移到辅助比特上从而实现可测量,测到的相位符合任意子统计。此外,研究人员用态注入的方式制备了含9和25个比特的逻辑态,对应码距为3和5的表面码,并演示了逻辑测量和纠错,逻辑制备和测量错误略低于物理比特的错误均值,但还需进一步提高相干时间并缩短周期,才可能实时纠错。

该工作给出的用浅电路实现环曲面码本征态的方法,可以扩展到其他拓扑有序态,研究逻辑比特态相干特性的方法也可用于量子纠错等的研究。

论文信息:https://arxiv.org/abs/2103.06720v1

English

English OA

OA Email

Email 登录

登录